# Journal of Advanced Research in Fluid Mechanics and Thermal Sciences

Journal homepage: www.akademiabaru.com/arfmts.html ISSN: 2289-7879

Open Access

# Thermal Impact of Heat Spreader Co-Planarity to Electronic Packaging

Pang Shi Shiang<sup>1,2,\*</sup>, Mohd Zulkifly Abdullah<sup>3</sup>

<sup>1</sup> Broadcom Ltd, 11900 Bayan Lepas, Penang, Malaysia

<sup>2</sup> School of Aerospace Engineering, Universiti Sains Malaysia, 14300 Nibong Tebal, Penang, Malaysia

<sup>3</sup> School of Mechanical Engineering, Universiti Sains Malaysia, 14300 Nibong Tebal, Penang, Malaysia

| ARTICLE INFO                                                                                                                                          | ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Article history:</b><br>Received 4 July 2019<br>Received in revised form 13 March 2020<br>Accepted 19 March 2020<br>Available online 30 April 2020 | This study presents the thermal impact of heat spreader co-planarity on the flip chip package with heat spreader. The co-planarity of heat spreader changes the thermal performance of the flip chip package significantly, especially the junction-to-case thermal resistance of the package. A numerical study using ANSYS lcepak was conducted to investigate the thermal degradation of heat spreader with concave and convex deflection up to 0.12 mm. The result indicates that the concave deflection causes improvement while convex deflection causes degradation in junction-to-case thermal resistance of the flip chip package. The outcome of the study recommends the co-planarity tolerance for the heat spreader shall not be greater than 0.07 mm for a 60 mm x 60 mm flip chip package with the dissipation power of 150 W. |

| <i>Keywords:</i><br>Electronic Packaging Cooling; Heat<br>Spreader Co-Planarity; CFD                                                                  | Copyright © 2020 PENERBIT AKADEMIA BARU - All rights reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

#### 1. Introduction

The thermal characterization data for the electronic package such as junction-to-ambient ( $\Theta_{JA}$ ), junction-to-board ( $\Theta_{JB}$ ) and junction-to-case ( $\Theta_{JC}$ ) thermal resistances are commonly found in any electronic packaging datasheet.  $\Theta_{JA}$  value is essential to the end user during the heat sink selection [1] in the system design and to determine whether a natural convection or forced air convection cooling design is required. While  $\Theta_{JB}$  and  $\Theta_{JC}$  are crucial to the end user especially when the product designer wants to predict the maximum junction temperature (T<sub>J</sub>) of the electronic package in the system using Computational Fluid Dynamics (CFD) simulation. Most of the CFD simulation tools allow packaging modelling simplification by using two resistance model or also known as 2R model without the need to build a detail packaging model in the simulation as presented by Shidore [2-4]. The 2R is defined in JESD15-3 [5] and the 2R refers to the  $\Theta_{JB}$  and  $\Theta_{JC}$  values provided in the package datasheet.

\* Corresponding author.

E-mail address: shi-shiang.pang@broadcom.com (Pang Shi Shiang)

https://doi.org/10.37934/arfmts.71.1.19

Normally, thermal characterization analyses are carried out with the assumptions that all parts in the packaging are at nominal and perfect conditions. There is no co-planarity issue on all the parts of the flip chip package. The thermal interface material 1 (TIM1) as defined by Gowda [6] is assumed to fill up the gap between the silicon die and the heat spreader perfectly without any void. However, in reality, the warpage can be easily found on the heat spreader and it becomes even more severe when the package size is bigger with heat spreader of larger surface area. The co-planarity of the heat spreader creates voids on TIM1 material that eventually degrades the heat transfer from the silicon die to the heat spreader [7-9]. As a result, the junction-to-case thermal resistance increases significantly.

Typically, for a flip chip package with a heat spreader,  $\Theta_{JC}$  in the range of 0.05 to 0.10 °C/W [10] depends on the design of the package. For a high power packaging, a small variation of  $\Theta_{JC}$  value will cause a significant difference on T<sub>J</sub>. For instance, a package with a dissipation power of 300 W with variation of 0.05 °C/W on  $\Theta_{JC}$  will cause 15 °C difference on the junction temperature. Therefore, the accuracy of  $\Theta_{JC}$  value is very important in order to prevent an overestimation or underestimation of the maximum junction temperature of the package that will eventually increase the product cost.

#### 2. Thermal Analysis with Computational Fluid Dynamics (CFD) Approach

A 60 mm x 60 mm flip chip package with heat spreader of 1 mm in thickness and 150 W uniform power map is used as the test vehicle for the thermal characterization analysis. All the components are modelled in detail, except the substrate, solder bumps with underfill and solder balls are lumped models. The lumped models are assigned with estimated equivalent orthotropic thermal conductivities as summarized in Table 1. The 2s2p board is modelled according to JEDEC specification of JESD51-9 [11], modelled in detail with traces and metal layers imported from the board design file.

| Lumped Models summary            |  |  |

|----------------------------------|--|--|

| Orthotropic Thermal Conductivity |  |  |

| (47.2 7.6 47.2) W/m.K            |  |  |

| (0.966 20.319 0.966) W/m.K       |  |  |

| (0.05 18.48 0.05) W/m.K          |  |  |

|                                  |  |  |

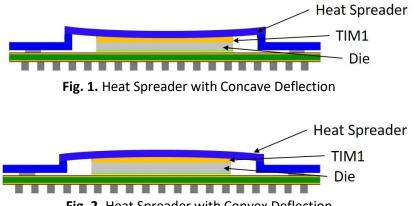

The concave and convex deflections up to 0.12 mm are investigated under the heat spreader coplanarity study. The heat spreaders with concave and convex deflections are modelled separately as CAD geometries using Solidworks before being imported to ANSYS Icepak. The heat spreaders with concave and convex deflections are shown in Figure 1 and Figure 2 respectively.

Fig. 2. Heat Spreader with Convex Deflection

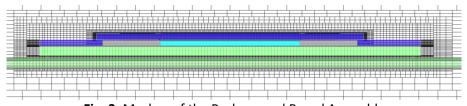

Multiple non-conformal mesh assemblies are assigned in the model in order to generate sufficient tiny meshes to capture the deflection profile and slowly transition to coarser meshes to the JEDEC 2s2p board and then the test fixture. The meshes generated are shown in Figure 3.

Fig. 3. Meshes of the Package and Board Assembly

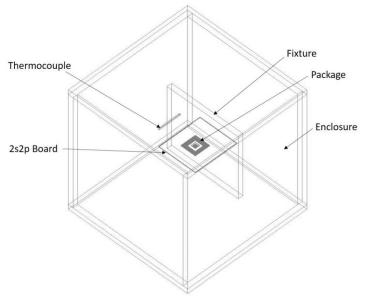

### 2.1 $\Theta_{JA}$ Thermal Characterization Analysis

The simulation model for  $\Theta_{JA}$  thermal characterization is constructed according to the standard test methodology that is defined by JC-15 Committee in JESD51-2 [12] and JESD51-2A [13] as shown in Figure 4.  $\Theta_{JA}$  simulation runs at natural convection environment at ambient temperature of 25 °C until steady state is reached. The setup of this simulation can be summarized as Table 2.

Fig. 4.  $\Theta_{JA}$  Simulation Modelling

| Table 2                               |                           |  |  |

|---------------------------------------|---------------------------|--|--|

| $	heta_{JA}$ Simulation Setup summary |                           |  |  |

| Simulation Setup                      | Mode                      |  |  |

| Flow                                  | On                        |  |  |

| Temperature                           | On                        |  |  |

| Radiation                             | On                        |  |  |

| Gravity                               | On                        |  |  |

| Flow Regime                           | Turbulent – Zero Equation |  |  |

$\Theta_{JA}$  under these conditions can be determined from Eq. (1) below [12,13].

$$\Theta_{JA} = \frac{T_J - T_A}{P_H}$$

(1)

where the  $T_J$  is junction temperature of the device at steady state,  $T_A$  is the ambient temperature and  $P_H$  is the power dissipation of the device respectively.

#### 2.2 OJB Thermal Characterization Analysis

The  $\Theta_{JB}$  simulation model is constructed based on the JEDEC standard, defined in JESD51-8 [14] as shown in Figure 5. The ring style cold plates as defined in JEDEC are simplified by removing the water channels from the cold plates. The water channels are being replaced by applying constant temperature wall boundary conditions around the exterior surfaces of the top and bottom cold plates to mimic the constant temperature from the water cooling effect. Therefore, the junction-to-board thermal characterization is simulated under pure conduction heat transfer until steady state is reached with the simulation setup as summarized in Table 3.

Fig. 5.  $\Theta_{JB}$  Simulation Modeling

| Table 3                                                      |      |  |  |

|--------------------------------------------------------------|------|--|--|

| $	heta_{^{JB}}$ and $	heta_{^{Jc}}$ Simulation Setup summary |      |  |  |

| Simulation Setup                                             | Mode |  |  |

| Flow                                                         | Off  |  |  |

| Temperature                                                  | On   |  |  |

| Radiation                                                    | Off  |  |  |

| Gravity                                                      | Off  |  |  |

| Flow Regime                                                  | N/A  |  |  |

$\Theta_{JB}$  under these conditions can be determined from Eq. (2) below [14].

$$\Theta_{JB} = \frac{T_J - T_B}{P_H} \tag{2}$$

where the  $T_J$  is the junction temperature of the device at steady state,  $T_B$  is the board temperature and  $P_H$  is the power dissipation of the device respectively.

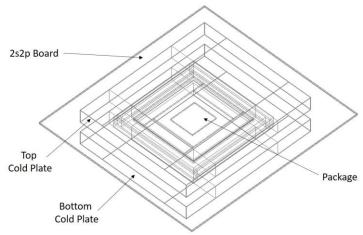

#### 2.3 Θ<sub>JC</sub> Thermal Characterization Analysis

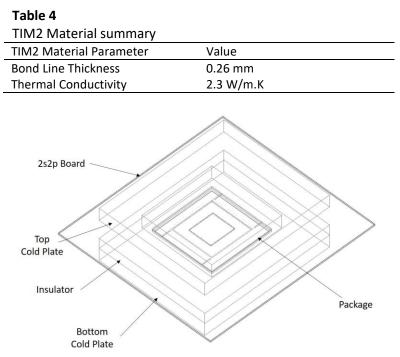

Similar to  $\Theta_{JB}$  simulation model, the  $\Theta_{JC}$  simulation model is constructed based on the test setup used in DELPHI compact model project as shown in Figure 6. The water channels of the cold plates are removed and replaced by constant temperature wall boundary conditions around the top and

bottom cold plates exterior surfaces to mimic the constant temperature from the water cooling effect. The TIM2 material is applied between the package and the top cold plate. The TIM2 material's parameters are summarized in Table 4.  $\Theta_{JC}$  characterization is simulated under pure conduction heat transfer until steady state is reached with the simulation setup similar to  $\Theta_{JB}$  simulation shown in Table 3.

Fig. 6.  $\Theta_{JC}$  Simulation Modeling

$\Theta_{JC}$  under this condition can be determined from Eq. (3) below.

$$\Theta_{JC} = \frac{T_J - T_C}{P_H} \tag{3}$$

where the  $T_J$  is the junction temperature of the device at steady state,  $T_C$  is the case temperature and  $P_H$  is the power dissipation of the device respectively.

#### 3. Results

Several simulations are carried out to investigate the thermal impact of heat spreaders with concave and convex deflections up to 0.12 mm in the flip chip package. The thermal resistances in the graphs shown in this section are based on calculations of the simulated temperatures obtained from the simulations using Eq. (1)-(3).

#### 3.1 OJA Thermal Characterization Result

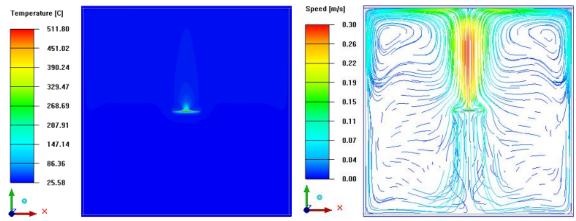

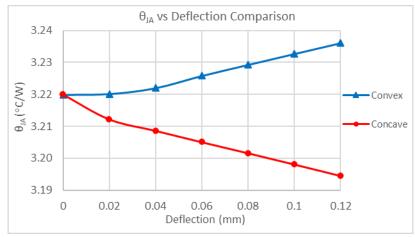

The temperature and airflow distribution patterns for this simulation are shown in Figure 7, respectively. Figure 8 shows  $\Theta_{JA}$  simulation results for convex and concave deflections from 0 to 0.12 mm. Results show that  $\Theta_{JA}$  improved by concave deflection while degraded by convex deflection. Nevertheless, the improvement and degradation are less than 1% if comparing both  $\Theta_{JA}$  at 0.12 mm

deflection to zero deflection. 1% of degradation equals to rise in junction temperate by 5  $^{\circ}$ C in the package with a dissipation power of 150 W.

Fig. 7.  $\Theta_{JA}$  Simulation Temperature Distribution (right) and Airflow Pattern (left)

Fig. 8.  $\Theta_{JA}$  vs Deflection Simulation Data Comparison

## 3.2 OJB Thermal Characterization Result

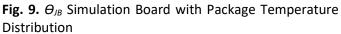

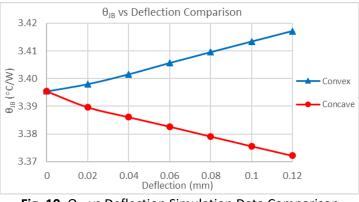

The temperature distribution of the package and board assembly for  $\Theta_{JB}$  simulation is shown in Figure 9.  $\Theta_{JB}$  simulation results show the similar trends as  $\Theta_{JA}$  as shown in Figure 10. Both convex and concave deflections cause variation of less than 1% if comparing  $\Theta_{JB}$  at 0.12 mm deflection to zero deflection. 1% variation of  $\Theta_{JB}$  equals to 5 °C variation of junction temperature in the package with a dissipation power of 150 W.

Fig. 10.  $\Theta_{JB}$  vs Deflection Simulation Data Comparison

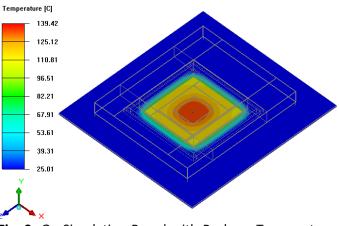

#### 3.3 OJC Thermal Characterization Result

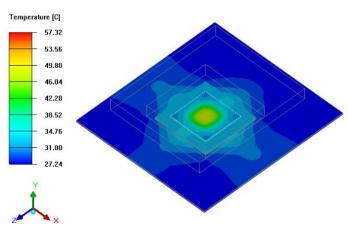

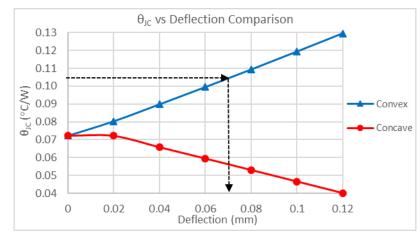

The temperature distribution for  $\Theta_{JC}$  simulation is shown in Figure 11. The convex deflection causes significant degradation while concave deflection improves the  $\Theta_{JC}$  of the flip chip package according to the simulation results as shown in Figure 12. If the targeted degradation is less than 5 °C of variation in junction temperature, junction-to-case thermal resistance must not be greater than 0.105 °C/W which leads to deflection of 0.07 mm referring to chart in Figure 12.

**Fig. 11.**  $\Theta_{JC}$  Simulation Board with Package Temperature Distribution

Fig. 12.  $\Theta_{JC}$  vs Deflection Simulation Data Comparison

The concave profile reduces the BLT while the convex profile increases the BLT of the TIM1 material in the flip chip package. According to Fourier's Law of heat transfer [15], the rate of heat conduction is inversely proportional to the thickness of medium, which is the BLT of TIM1 material in this case. Therefore, the results are compliance to Fourier's Law.

#### 4. Conclusions

It can be concluded that both the concave and convex deflections up to 0.12 mm on the heat spreaders do not cause significant degradations to the  $\Theta_{JA}$  and  $\Theta_{JB}$  of the flip chip package. However, the deflections on the heat spreader change the  $\Theta_{JC}$  significantly.  $\Theta_{JC}$  is approximately doubled if comparing the  $\Theta_{JC}$  at 0.12 mm convex deflection to zero deflection. In order to not exceed 5 °C increase of the junction temperature due to the deflection of the heat spreader, acceptable coplanarity tolerance of the heat spreader should not be greater than 0.07 mm for a 60 mm x 60 mm flip chip package with 150 W dissipation power.

#### Acknowledgement

The authors would like to acknowledge the sponsorship and resources provided by Broadcom Ltd for the completion of this study. The technical advice of Broadcom Ltd employees, Mr Sam Karikalan and Dr Zeki Celik are greatly appreciated.

#### References

- [1] Lee, Seri. "How to Select a Heat Sink." *Electronics Cooling*, 1995. https://www.electronicscooling.com/1995/06/how-to-select-a-heat-sink/.

- [2] Shidore, Sarang. "Compact thermal modeling in electronics design." *Electronics Cooling* 13, no. 2 (2007): 22.

- Shidore, Sarang, Vance Adams, and T. T. Lee. "A study of compact thermal model topologies in CFD for a flip chip plastic ball grid array package." *IEEE Transactions on Components and Packaging Technologies* 24, no. 2 (2001): 191-198. https://doi.org/10.1109/6144.926382

- Shidore, Sarang, and Tien Yu Tom Lee. "A comparative study of the performance of compact model topologies and their implementation in CFD for a plastic ball grid array package." *Journal of Electronics Packaging* 123, no. 3 (2001): 232-237.

https://doi.org/10.1115/1.1349423

- [5] JESD15-3. "Two-Resistor Compact Thermal Model Guideline." JEDEC, 2008.

- [6] Gowda, Arun, Sandeep Tonapi, Brad Reitz, and Gregory Gensler. "Choosing the right thermal interface material." *Advanced Packaging* 14, no. 3 (2005): 14-18.

- [7] Mahajan, Ravi, C. Chiu, and Ravi Prasher. "Thermal interface materials: a brief review of design characteristics and materials." *Electronics Cooling* 10, no. 1 (2004): 10.

- [8] Prasher, Ravi. "Thermal interface materials: historical perspective, status, and future directions." Proceedings of the IEEE 94, no. 8 (2006): 1571-1586. <u>https://doi.org/10.1109/JPROC.2006.879796</u>

- [9] Ramos-Alvarado, Bladimir, David Brown, Xiuping Chen, Bo Feng, and G. P. Peterson. "On the assessment of voids in the thermal interface material on the thermal performance of a silicon chip package." *Microelectronics Reliability* 53, no. 12 (2013): 1987-1995.

- https://doi.org/10.1016/j.microrel.2013.05.006

- [10] Galloway, Jesse, and Eduardo de los Heros. "Developing a Theta<sub>JC</sub> standard for electronic packages." In 2018 34th Thermal Measurement, Modeling & Management Symposium (SEMI-THERM), pp. 170-175. IEEE, 2018. <u>https://doi.org/10.1109/SEMI-THERM.2018.8357370</u>

- [11] JESD51-9. "Test Boards for Area Array Surface Mount Package Thermal Measurements." JEDEC, 2000.

- [12] JESD51-2. "Integrated Circuits Thermal Test Method Environmental Conditions Natural Convection (Still Air)." *JEDEC*, 1995.

- [13] JESD51-2A. "Integrated Circuits Thermal Test Method Environmental Conditions Natural Convection (Still Air)." *JEDEC*, 2008.

- [14] JESD51-8. "Integrated Circuits Thermal Test Method Environmental Conditions Junction-to-Board." JEDEC, 1999.

- [15] Çengel, Yunus A. Heat Transfer: A Practical Approach Second Edition (New York: McGraw-Hill, 2004).